GEM5中添加一个简单的IO模块

==================

近期想要在Gem5中模拟ORAM(Oblivious RAM)的算法,因此开始折腾起了Gem5。

ORAM简介

为了保护数据安全,我们经常对数据进行加密再进行存储。但是令人遗憾的是,很多时候,黑客可以通过大量统计CPU访存来总结出规律,从而推测出敏感信息。ORAM就是为了解决这个问题而诞生的。因此ORAM通常会需要在内存控制器之前对我们的访存地址或内容进行一些操作,来隐藏我们的访问模式。

新增一个简单的IO模块

为了实现上述目的,我们需要在gem5中添加一个IO传输模块,用于实现ORAM算法。在这里我们暂时先在gem5中新增一个简单的IO传输模块,目前这一模块的功能十分单一,它在内存总线和内存控制器之间,用于接收内存控制器的数据,并将这一数据原封不动地传输给内存控制器。之后ORAM算法将被添加到这一模块中,ORAM算法会将从内存总线接收到的数据包进行处理再传送给内存控制器。

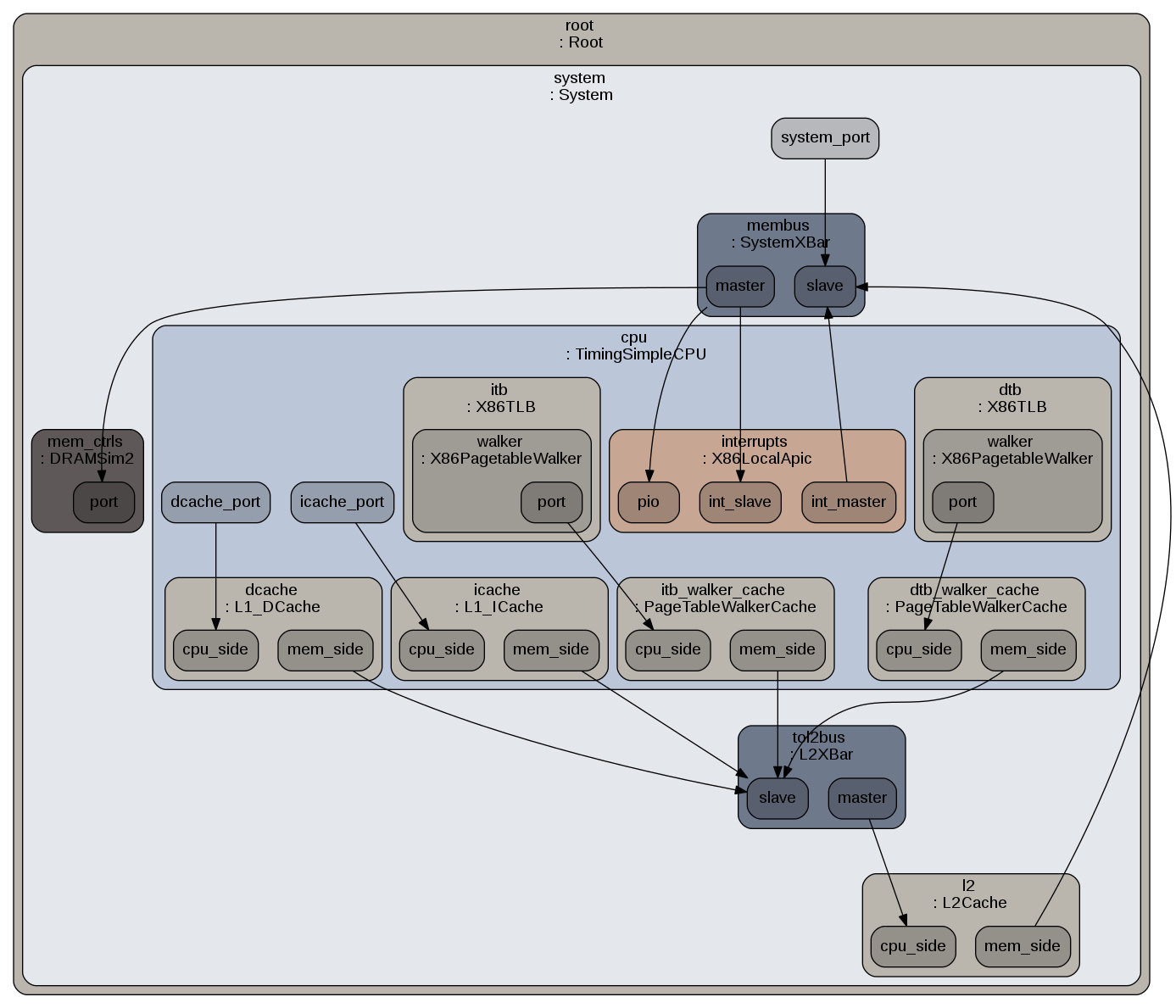

如图1所示的gem5配置图,在新增模块之前,CPU发出的消息经过L1_DCache->L2XBar->L2Cache->SystemXBar->DRAMSim2。我们计划在SystemXBar(membus)和DRAMSim2(mem_ctrls)之间添加一个ORAM新模块。

图1 gem5输出的默认系统配置图

1 | 1. 在src目录下新建ORAM目录 |

接下来我们需要修改se.py来将我们新增的这个模块加入到我们的系统配置中去。首先我们在cofigs/commom/MemConfig.py中修改1

2

3

4

5

6

7

8

9# Connect the controllers to the membus

for i in xrange(len(subsystem.mem_ctrls)):

if opt_mem_type == "HMC_2500_1x32":

subsystem.mem_ctrls[i].port = xbar[i/4].master

# Set memory device size. There is an independent controller for

# each vault. All vaults are same size.

subsystem.mem_ctrls[i].device_size = options.hmc_dev_vault_size

else:

subsystem.mem_ctrls[i].port = xbar.master

为1

2

3

4

5

6

7

8

9# Connect the controllers to the membus

for i in xrange(len(subsystem.mem_ctrls)):

if opt_mem_type == "HMC_2500_1x32":

subsystem.mem_ctrls[i].port = xbar[i/4].master

# Set memory device size. There is an independent controller for

# each vault. All vaults are same size.

subsystem.mem_ctrls[i].device_size = options.hmc_dev_vault_size

# else:

# subsystem.mem_ctrls[i].port = xbar.master

这是因为我们需要在后面手工设置内存控制器连接我们新增的模块,而它默认会连接到内存控制器上,因此需要将其默认的连接取消掉,否则重复连接会导致错误。

接下来修改configs/example/se.py,在文件中找到如下代码行1

MemConfig.config_mem(options, system)

将其修改为1

2

3

4MemConfig.config_mem(options, system)

system.hello=ORAMobj()

system.mem_ctrls[0].port=system.hello.mem_side

system.hello.cache_side=system.membus.master

此外所需要注意的上面的例子中的cache_side和mem_side分别为模块的master端和slave端。

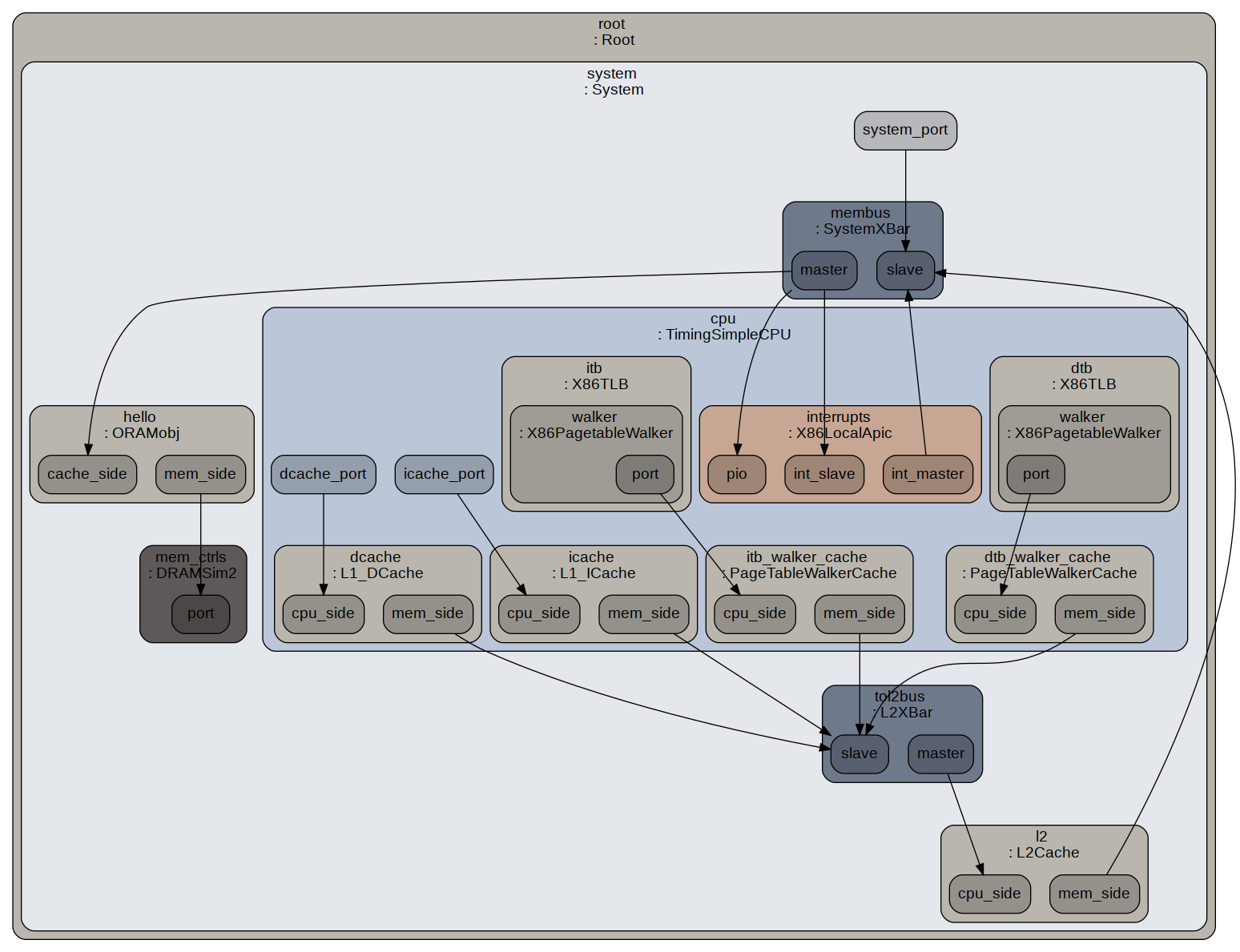

完成之后再次进行编译即可看到最终的效果了。而我们的m5out则会变成如图2所示的结构。可以看到相比于之前的系统配置,我们在里面新增了一个ORAM模块

图2 新增一个IO模块后的配置图